mirror of

https://openbeagle.org/beagley-ai/beagley-ai.git

synced 2026-05-06 13:34:29 +00:00

main

Signed-off-by: Robert Nelson <robertcnelson@gmail.com>

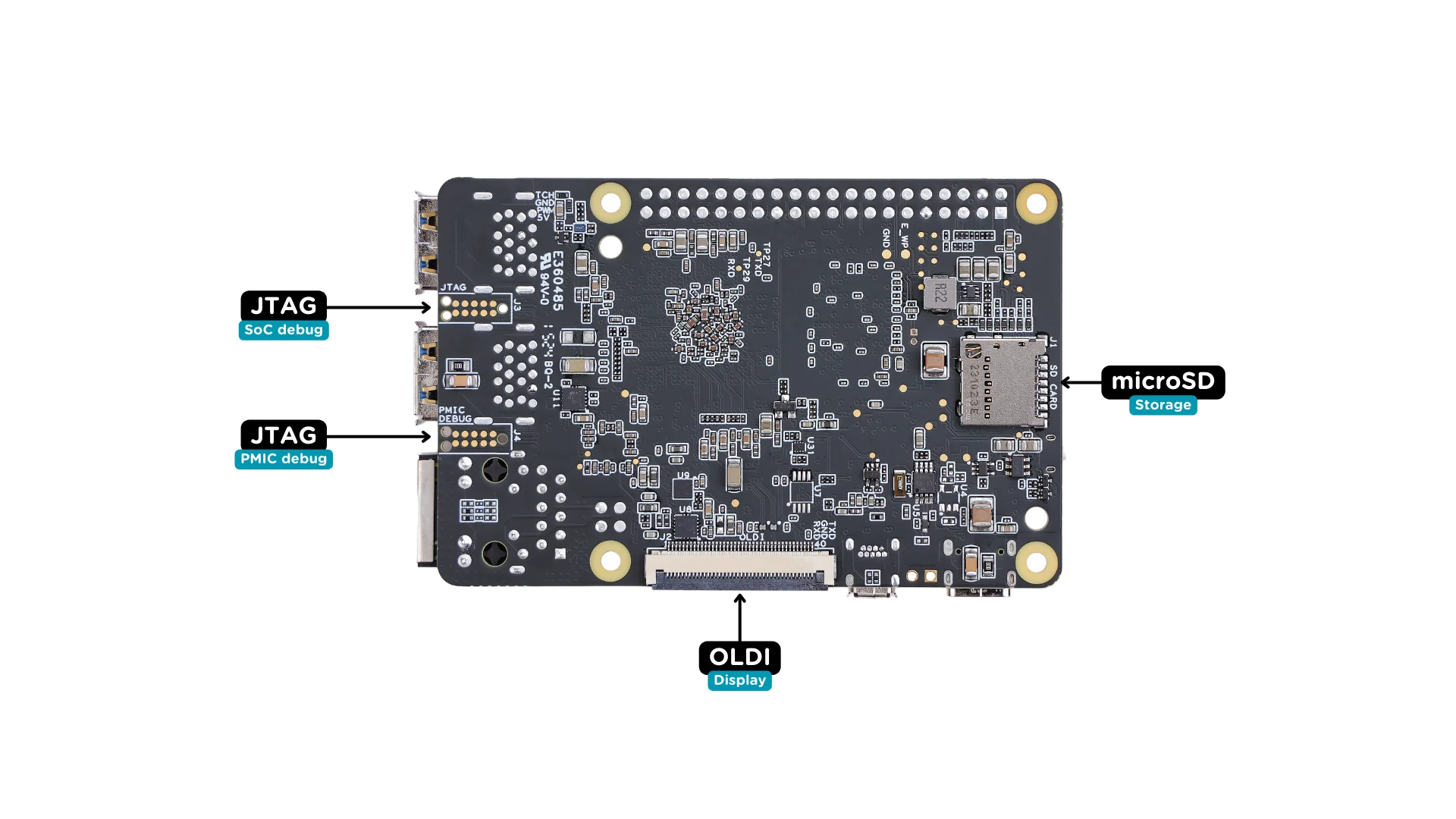

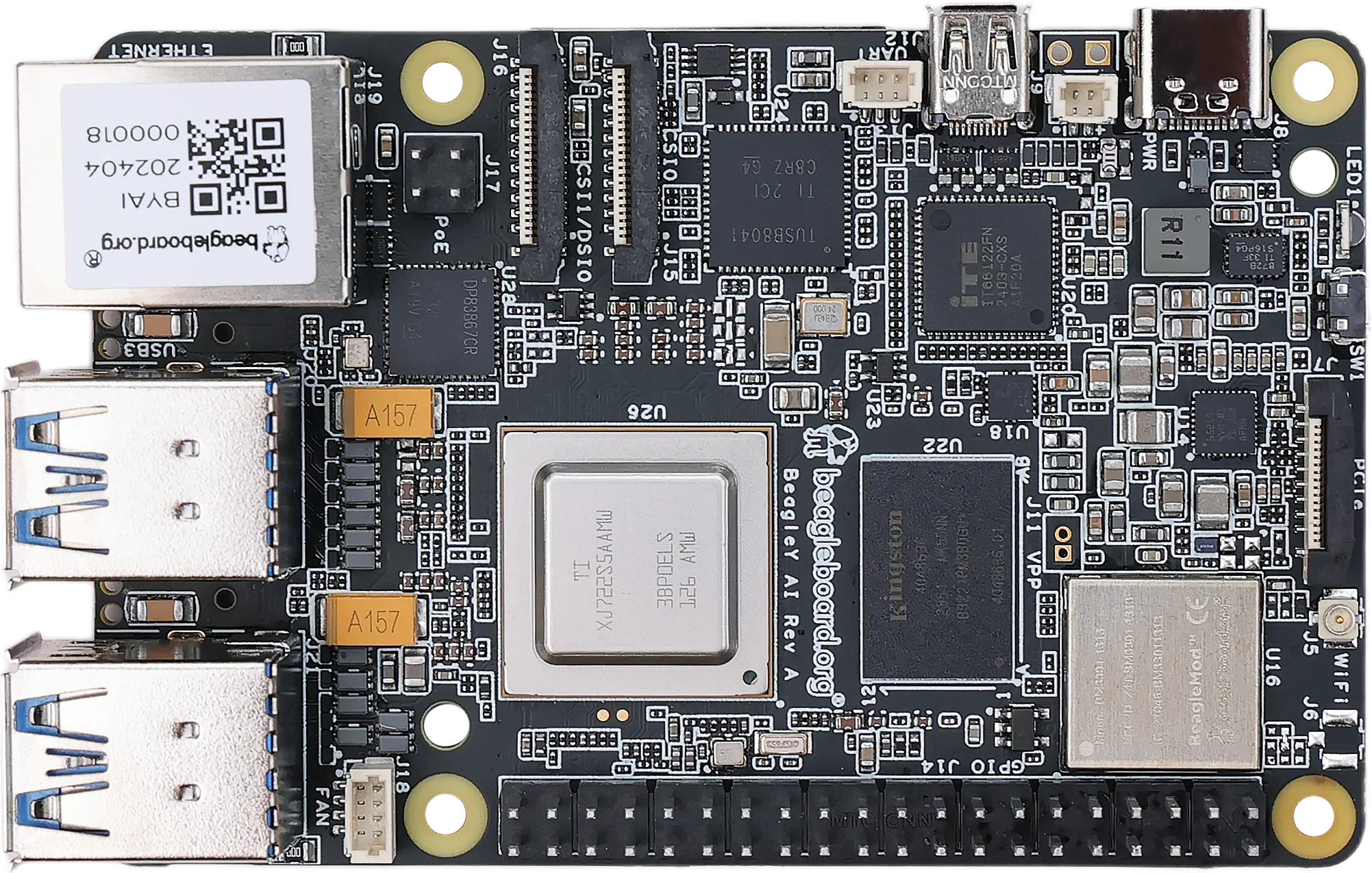

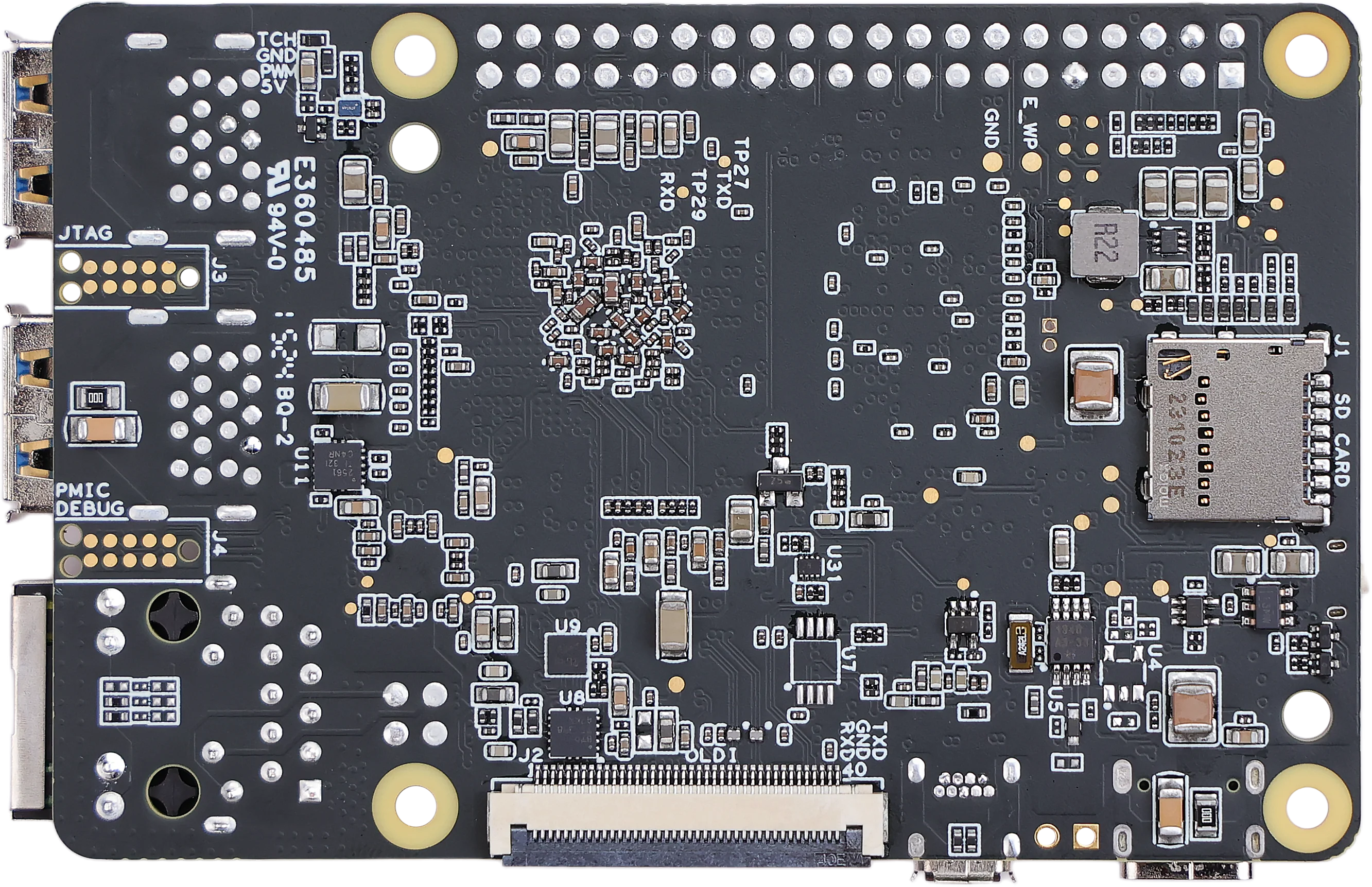

BeagleY®-AI

BeagleY®-AI is a powerful 64-bit quad core single board computer with GPU, DSP, and vision/deep learning accelerator.

| Front | Back |

|---|---|

|

|

OSHW Certification: https://certification.oshwa.org/us002616.html

Features and purchase information at https://beagley-ai.org

Features

| Feature | Description |

|---|---|

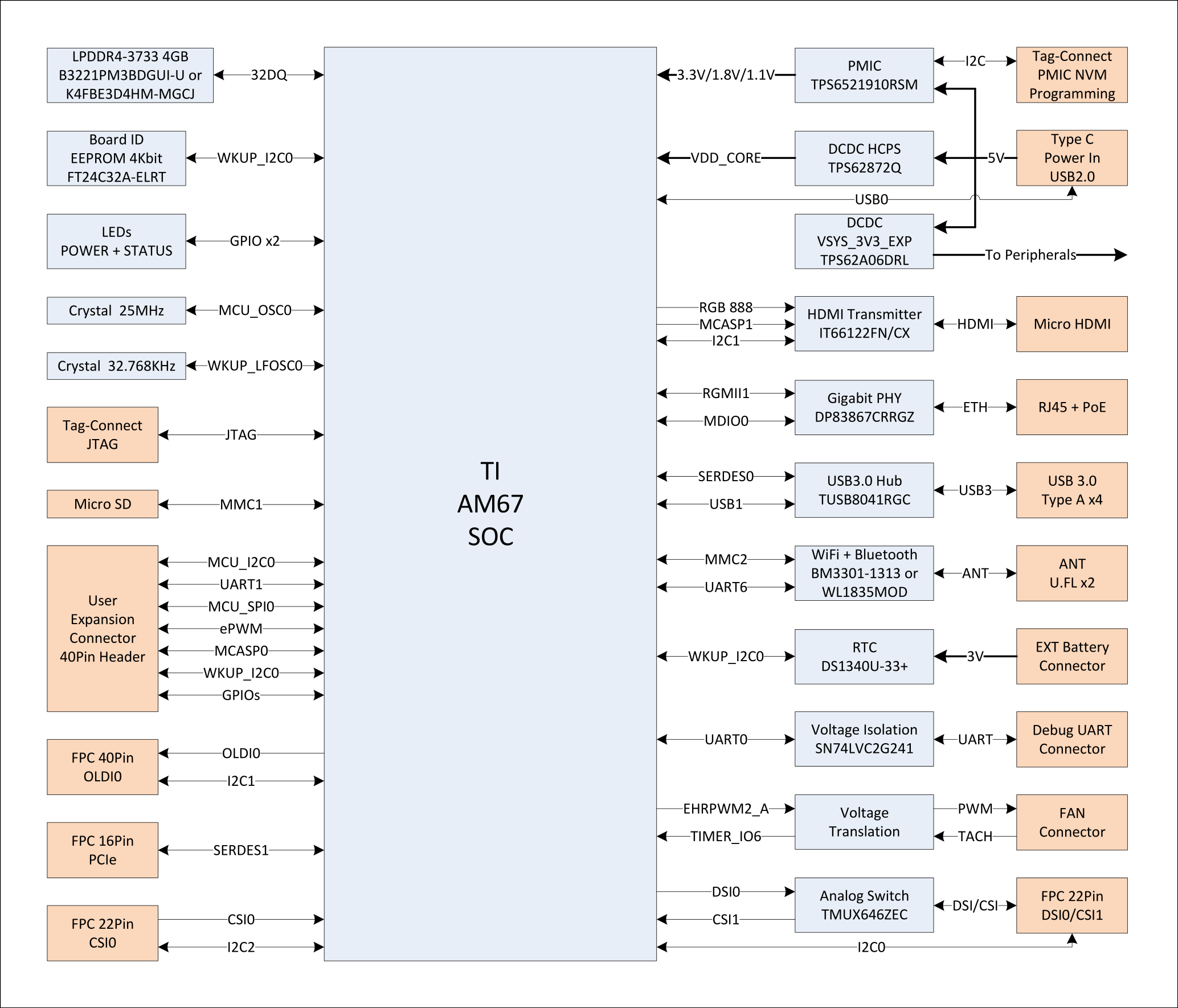

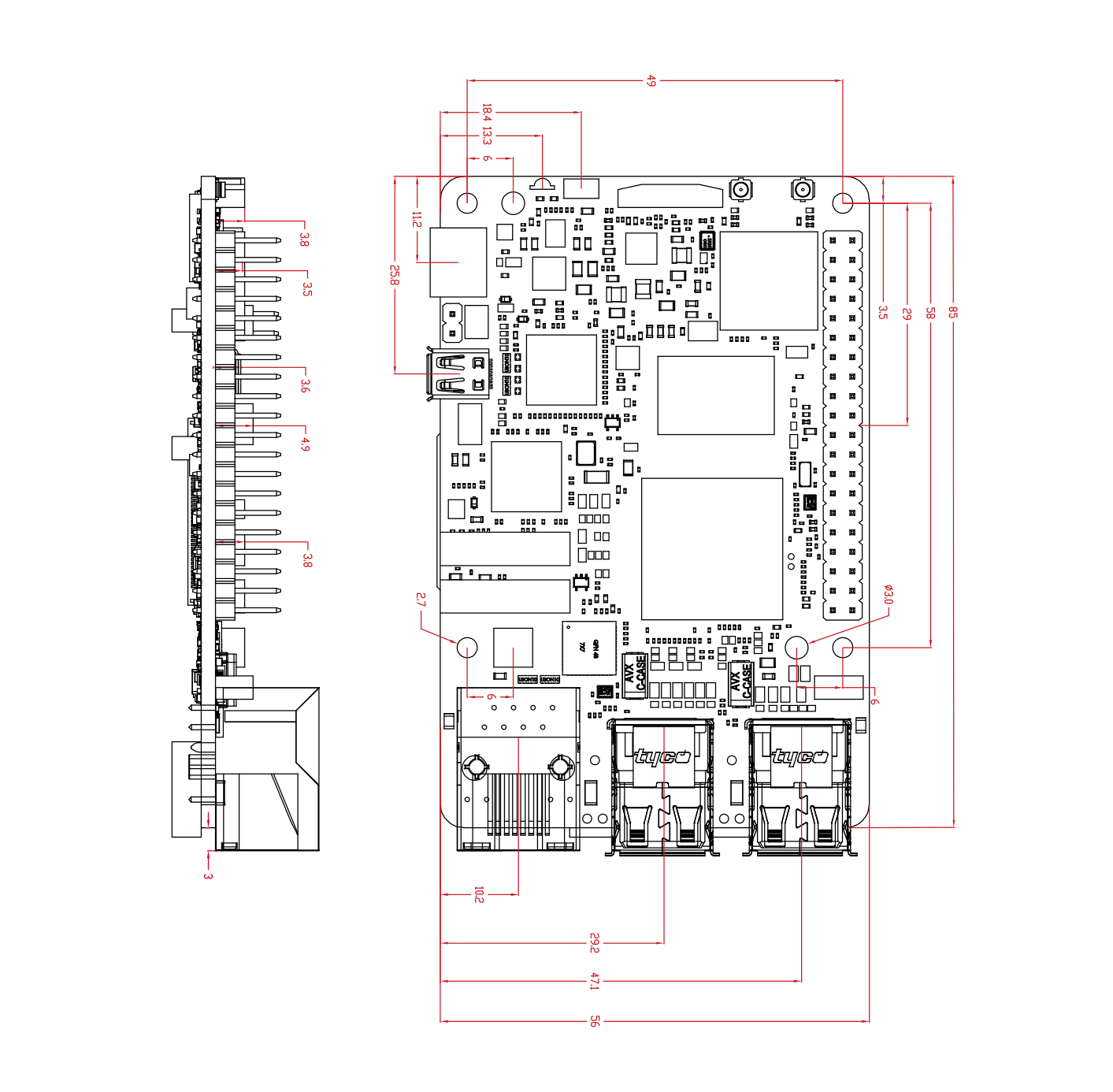

| Processor | TI AM67 with Quad core 64-bit Arm® Cortex®-A53, GPU, DSP, and vision/deep learning accelerators |

| RAM | 4GB LPDDR4 |

| Wi-Fi | BeagleBoard BM3301, 802.11ax Wi-Fi |

| Bluetooth | Bluetooth Low Energy 5.4 (BLE) |

| USB Ports | 4 x USB 3.0 TypeA ports supporting simultaneous 5Gbps operation, 1 x USB 2.0 TypeC supports USB 2.0 device |

| Ethernet | Gigabit Ethernet, with PoE+ support (requires separate PoE+ HAT) |

| Camera/Display | 1 x 4-lane MIPI camera/display transceivers, 1 x 4-lane MIPI camera |

| Display Output | 1 x HDMI display, 1 x OLDI display |

| Real-time Clock (RTC) | Supports an external button battery for power failure time retention. it is only populated on EVT samples. |

| Debug UART | 1 x 3-pin debug UART |

| Power | 5V/5A DC power via USB-C, with Power Delivery support |

| Power Button | On/Off included |

| PCIe Interface | PCI-Express® Gen3 x 1 interface for fast peripherals (requires separate M.2 HAT or other adapter) |

| Expansion Connector | 40-pin header |

| Fan connector | 1 x 4-pin fan connector, supports PWM speed control and speed measurement |

| Storage | microSD card slot, with support for high-speed SDR104 mode |

| Tag Connect | 1 x JTAG, 1 x Tag Connect for PMIC NVM Programming |